ECE :: Digital Electronics

-

A two-input OR gate is designed for positive logic. However, it is operated with negative logic. The resulting logic operation will then be

-

A clock signal driving a 6-bit ring counter has a frequency of 1 MHz. How long is each timing bit high?

-

A twisted ring counter consisting of 4 FF will have

-

Assertion (A): In a serial in-serial out shift register, access is available only to the left most or right most flip flops

Reason (R): If the output of a shift register is feedback to serial input it can be used as a ring counter.

-

IC counters are

-

The method used to transfer data from I/O units to memory by suspending the memory-CPU data transfer for one memory cycle is called

-

Out of SAM and RAM

-

Bipolar IC memories are fabricated using

-

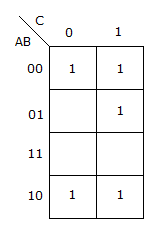

For K map of the given figure the simplified Boolean expression is

-

Choose the appropriate turn on and turn off time of a FET

Whatsapp

Whatsapp

Facebook

Facebook