ECE :: Network Analysis and Synthesis

-

Poor power factor

-

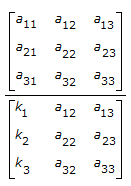

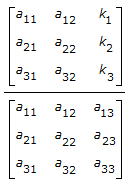

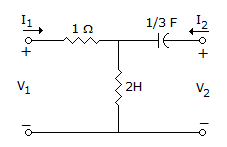

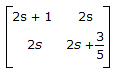

If two networks are cascaded then

-

When a series RL circuit is switched on to a dc voltage, the rate of change of current is maximum at t = 0.

-

In a circuit containing a complex impedance, maximum power transfer takes place when load is

-

The resistance of a bulb at the time of full brightness is 1200 Ω. Then the resistance at room temperature is about

-

For a delayed half wave rectified wave, the average and rms values are lower than those for half wave.

-

A reactance function is always a quotient of

Whatsapp

Whatsapp

Facebook

Facebook