ECE :: Digital Electronics

-

TTL logic is preferred to DRL logic because

-

Assertion (A): Schottky transistors are preferred over normal transistors in digital circuits

Reason (R): A Schottky transistor when used as a switch, between cutoff and active region.

-

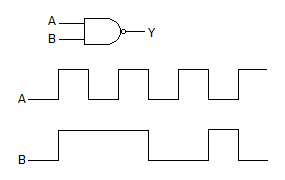

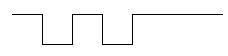

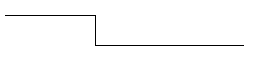

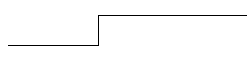

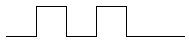

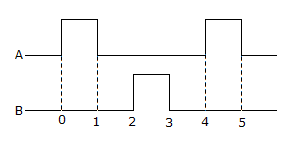

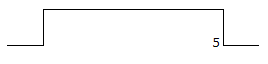

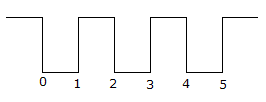

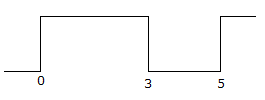

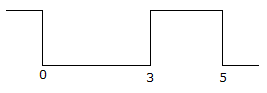

The inputs A and B of the given figure are applied to a two input NOR gate. The output waveform is

-

A parallel in-parallel out shift register can be used to introduce delay in digital circuits.

-

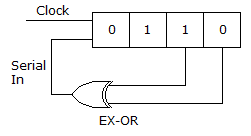

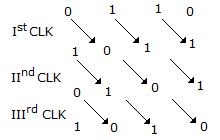

In following figure, the initial contents of the 4-bit serial in parallel out, right shift, shift register as shown in figure are 0110. After 3 clock pulses the contents of the shift register will be

-

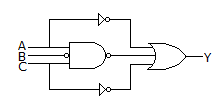

For the logic circuit of the given figure, the minimized expression is

-

Assertion (A): In totem pole output the output impedance is low.

Reason (R): TTL gate with active pull up should not be used in wired AND connection.

-

A 4 bit synchronous counter uses flip flops with a delay time of 15 ns each. The time required for change of state is

Whatsapp

Whatsapp

Facebook

Facebook

+

+