ECE :: Digital Electronics

-

Out of 5 M x 8, 1 M x 16, 2 M x 16 and 3M x 8 memories, which memory can store more bits?

-

A 6 bit ladder A/D converter has input 101001. The output is (assume 0 = 0 V and 1 = 10 V)

-

A ripple counter has 4 bits and uses flip flops with propagation delay time of 25 ns. The maximum possible time for change of state will be

-

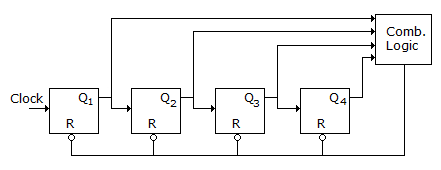

The counter shown in the given figure is built using 4 -ve edge triggered toggle FFs. The FF can be set asynchronously when R = 0. The combinational logic required to realize a modulo-13 counter is

-

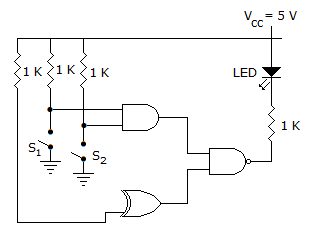

In the figure, the LED

-

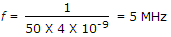

A 4 bit ripple counter uses flip flops with propagation delay of 50 ns each. The maximum clock frequency which can be used is

-

An AND gate has two inputs A and B and one inhibit input S. Out of total 8 input states, output is 1 in

-

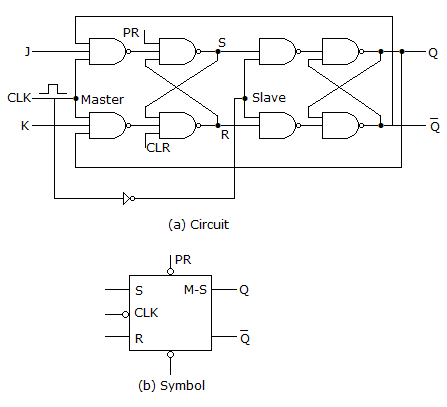

In a JK Master slave flip flop

Whatsapp

Whatsapp

Facebook

Facebook

10 j 6.41 V.

10 j 6.41 V. .

.