ECE :: Digital Electronics

-

Assertion (A): Master slave JK flip flop is commonly used in high speed synchronous circuitry

Reason (R): Master slave JK flip flop uses two JK flip flops in cascade.

-

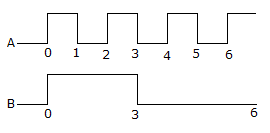

Inputs A and B of the given figure are applied to a NAND gate. The output is LOW

-

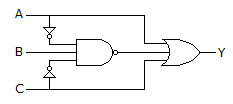

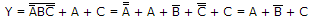

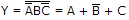

For the NMOS gate in the given figure, F =

-

The resolution of 4 bit counting ADC is 0.5 volt, for an Analog input of 6.6 volts. The digital output of ADC will be

-

Read the following statements

- The circuitry of ripple counter is more complex than that of synchronous counter.

- The maximum frequency of operation of ripple counter depends on the modulus of the counter.

- The maximum frequency of operation of synchronous counter does not depend on the modulus of the counter.

Whatsapp

Whatsapp

Facebook

Facebook

.

.

.

.