ECE :: Network Analysis and Synthesis

-

Which of the following theorems enables a number of voltage (or current) sources to be combined directly into a single voltage (or current) source?

-

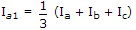

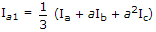

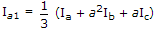

If Ia, Ib, Ic are line currents and Ia1 is the positive sequences component of Ia then

-

If the numerator of Z(s) is one degree higher than denominator, Z(s) has a pole at infinity.

-

An m derived low pass filter has fc = 1000 Hz, f∞ = 1250 Hz and m = 0.6. If m is increased, then

-

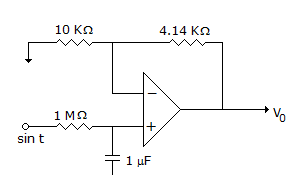

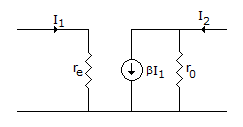

In the two ports network shown in the figure, Z12 and Z21 are, respectively

-

The design of wave filter is based on characteristic impedance which is

-

A system is said to be marginal stable if

-

Assertion (A): In state space analysis, capacitors are taken to be in tree.

Reason (R): State variable analysis is very suitable for computer solution.

Whatsapp

Whatsapp

Facebook

Facebook