ECE :: Exam Questions Paper

-

A 3 x 8 decoder with two enable inputs is to be used to address 8 blocks of memory. What will be the size of each memory block when addressed from a sixteen bit bus with two MSBs used to enable the decoder?

-

What is the purpose of a start in RS232 serial communication protocol?

-

Time delay produced by an instruction code given below using 2 MHz clock is:

MVI A, FFH

LOOP: DCR A

JNZ Loop -

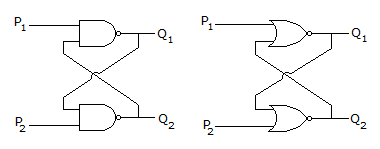

Refer to the NAND and NOR latches shown in the figure. The inputs (P1, P2) for both the latches are first made (0, 1) and then, after a few seconds, made (1, 1). The corresponding stable outputs (Q1, Q2) are

-

Consider the following two statements about the internal conditions in an n-channel MOSFET operating in the active region

S1: The inversion charge decreases from source to drain

S2: The channel potential increases from source to drain

Which of the following is correct? -

For what positive value of K does the polynomial s4 + 8s3 + 24s2 + 32s + K have roots with zero real parts?

-

Which of the following capabilities are available in a Universal Shift Register?

- Shift left

- Shift right

- Parallel load

- Serial add

Whatsapp

Whatsapp

Facebook

Facebook