ECE :: Digital Electronics

-

In 8085, usually the vector location and the next two memory location contain a JMP instruction. This allows the programs to branch to

-

In a positive-edge-triggered JK flip-flop, a low J and a low K produce __________ state. A high __________ on the rising edge of the clock.

-

The rate of change of digital signals between High and Low level is

-

Which of the following is best suited for parity checking and parity generation?

-

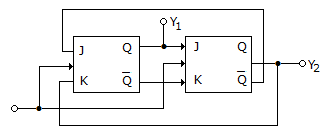

In the circuit shown below, the outputs Y1 and Y2 for the given initial condition Y1 = Y2 = 1 and after four input pulses will be

-

Assertion (A): Power drain of CMOS increases with operating frequency

Reason (R): All unused CMOS inputs should be tied either to a fixed voltage level (0 or VDD) or to another input.

Whatsapp

Whatsapp

Facebook

Facebook