ECE :: Digital Electronics

-

Commercial ECL gates use two ground lines and one negative supply to

-

Which of the following is incorrect?

-

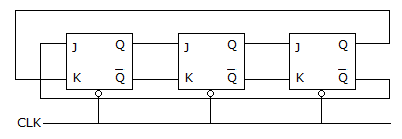

A 3 stage Johnson counter (ring) shown in figure is clocked at a constant frequency of fc from the starting state of Q0 Q1 Q2 = 101. The frequency of output Q0 Q1 Q2 will be

-

A depletion type NMOS is operated in enhancement mode. Vp = - 4 volts. For VGS = + 3 volts as VDS is increased, ID becomes nearly constant when Vps equals

-

Which one of the following is D/A conversion technique?

-

Assuming accumulator contain A 64 and the carry is set (1). What will accumulator (A) and carry (CY) contain after ANA A?

-

A number is expressed in binary 2's complement as 10011 decimal equivalent value is

-

In INHIBIT operation

Whatsapp

Whatsapp

Facebook

Facebook