ECE :: Digital Electronics

-

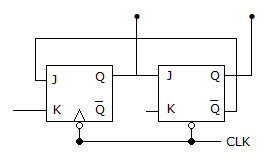

A 4 bit modulo 16 ripple counter uses JK flip-flops. If the propagation delay of each FF is 50 ns. The max. clock frequency that can be used is equal to

-

As the number of flip flops are increased, the total propagation delay of

-

In a 4 input OR gate, the total number of High outputs for the 16 input states are

-

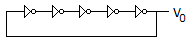

For the ring oscillator shown in the figure, the propagation delay of each inverter is 100 pico sec. What is the fundamental frequency of the oscillator output __________

-

Which of the following is not a characteristic of a flip flop?

-

For AB + A C + BC = AB + A C the dual form is

-

A DAC has full scale output of 5 V. If accuracy is ± 0.2% the maximum error for an output of 1 V is

Whatsapp

Whatsapp

Facebook

Facebook

.

. .

. = 10 mV.

= 10 mV.