Discussion :: GATE EEE

-

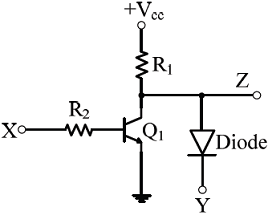

In the circuit shown below, Q1 has negligible collector-to-emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If Vcc is +5 V, X and Y are digital signals with 0 V as logic 0 and Vcc as logic 1, then the Boolean expression for Z is

Answer : Option B

Explanation :

-NA-

Be The First To Comment

.

. .

. .

.

Whatsapp

Whatsapp

Facebook

Facebook